# **SCIENTIFIC BULLETIN**

PHYSICAL AND MATHEMATICAL RESEARCH

ILMIY HABARNOMA FIZIKA-MATEMATIKA TADQIQOTLARI

2023 VOLUME 5 ISSUE 1

## ОГЛАВЛЕНИЕ

| <u>Физика</u>                                                                                                                                                                                                  |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>С.3. ЗАЙНАБИДИНОВ, А.С. САИДОВ, А.Й. БОБОЕВ, Б.М. ЭРГАШЕВ</b> Получения, морфология и фотоэлектрические свойства гетероструктуры $n$ -Si- $p$ -(Ge <sub>2</sub> ) $_{I$ - $x$ - $y$ (GaAs) $_x$ (ZnSe) $_y$ | 7  |

| <b>Н.Ф. ЗИКРИЛЛАЕВ, К.А. ИСМАЙЛОВ, С.З. ЗАЙНАБИДИНОВ, З.Т. КЕНЖАЕВ, Б.К. ИСМАЙЛОВ</b> Влияние легирования никелем на спектральную чувствительность кремниевых солнечных элементов                              | 16 |

|                                                                                                                                                                                                                | 10 |

| <b>М.Ш. ИСАЕВ, А.Т. МАМАДОЛИМОВ, Ш.К. АКБАРОВ</b> Структура приповерхностного слоя диффузионно-легированного кремния атомами хрома и кобальта                                                                  | 21 |

| M.B. TAGAEV, A.A. ABDREYMOV, U.D. BAIRAMOV Kremniyli p-n o'tishda mikroplazmalarning shakllanishi                                                                                                              | 27 |

| M.B. FOZILJONOV, I.N. KARIMOV, A.E. ABDIKARIMOV Influence of the local trapped charge in oxide to the gate - drain capacitance in a FinFET.                                                                    | 33 |

| Ш.Х. ЙУЛЧИЕВ, И.М. СОЛИЕВ, Х.Ж. МАНСУРОВ                                                                                                                                                                       |    |

| Рентгеноструктурные исследования кремния марки КДБ-20 с участием                                                                                                                                               | 37 |

| Техника                                                                                                                                                                                                        | 31 |

| Р.А. МУМИНОВ, В.Г. ДЫСКИН, О.Ф. ТУКФАТУЛЛИН, Б.Н. БУТУНБАЕВ, К.А. ДЖУМАМУРАТОВ К вопросу применения гидрофобных плёнок для пассивной очистки фронтальной поверхности фотоэлектрических модулей                 | 42 |

| С. ЗАЙНАБИДИНОВ, Б. УРМАНОВ, С. АЛИЕВ                                                                                                                                                                          |    |

| Разработка конструкции нового солнечного осветительного устройства                                                                                                                                             | 47 |

| С.С. НАСРИДДИНОВ, А.К. ХАМРАКУЛОВ, Н.Т. МОВЛОНОВ, М.И. МАННАНОВ                                                                                                                                                |    |

| Метод определения удельного сопротивления почвы                                                                                                                                                                | 53 |

| <b>Ш.А. ГУЛАМОВ, Г.М. МЎМИНОВА</b> Легирланган ва лнгирланмаган қўға ўсимлиги толаларини таййорлаш хамда уларнинг оптоелектроник хоссалари тадқиқ қилиш усуллари                                               | 58 |

| Математика                                                                                                                                                                                                     |    |

| А.К. УРИНОВ, Д.А. УСМОНОВ                                                                                                                                                                                      |    |

| Нелокальная задача для вырождающегося уравнения второго порядка, содержащего интегро-дифференциальный оператор дробного порядка с функцией бесселя в ядре                                                      | 64 |

| N. UMRZAQOV, I.S. ZAYNABIDDINOV                                                                                                                                                                                |    |

| On a pursuit differential game with integral constraints in $\mathbb{R}^n$                                                                                                                                     | 75 |

| <b>Д.Д. АХМЕДОВА</b> Динамические системы симплекса квадратичных гомеоморфизмов                                                                                                                                | 83 |

| Ф.А. ЮСУПОВ, Д.Д. АХМЕДОВА                                      |    |

|-----------------------------------------------------------------|----|

| Инвариантость некоторых стохастических квадратичных операторов  |    |

| неволтеррного типа в двухмерном симплексе                       | 87 |

| <u>Информатика</u>                                              |    |

| Р.К. АЗИМОВ, Б.Р. АЗИМОВ                                        |    |

| Машинали ўкитишда регрессия усуллари                            | 90 |

| М.К.МАХКАМОВ, Х.А.МАМАДАЛИЕВ, Ш.Ш.ХОЖИКУЛОВ                     |    |

| Метод Фурье для исследования распространения волны уплотнения в |    |

| трубопроводах установленном демпфером                           | 96 |

| Ғ.О. ТАЖИБАЕВ, М.М. МИРЗАЕВА, Ш.О. ТЎРАХОНОВА.                      |     |

|---------------------------------------------------------------------|-----|

| Юпқа пластина эгилиши масаласини интегралли усулда ечишда чегаравий |     |

| шартларга боғлиқ бўлган махсусликни эътиборга олиш                  | 104 |

| <u>-</u>                      | персоналии |     |

|-------------------------------|------------|-----|

| Академиг М. Мусахонов 80 ёшда |            | 111 |

| Правила оформления            |            |     |

| статьи                        |            | 113 |

UDK: 621.382.323

# Influence of the local trapped charge in oxide to the gate - drain capacitance in a finFET

<sup>1</sup>Foziljonov M.B., <sup>1</sup>Karimov I.N., <sup>2</sup> Abdikarimov A.E.

Получена 1 мая 2023 г. Принята к печати 25 мая 2023 г.

**Abstract:** In this paper, the influence of the local trapped charge in the gate oxide layer on the total of the capacity of gate-drain is studied. It was investigated that the approaching of the local trapped charge in the gate oxide layer towards the source influences the change in the density of electrons and holes in the drain-channel regions and electric capacity of drain-channel regions.

**Key words**: trapped charge, oxide-semiconductor region, density of electrons and holes, p-n junction, electric capacity, gate, drain and channel.

**Аннотация:** В данной работе исследуется влияние локальизованного заряда в оксидном слое затвора на емкость затвор-сток. Показано, что с приближением локального заряда в оксидном слое к истоку влияет на изменение плотности электронов и дырок в областях сток-канал и емкость областей сток-канал.

**Ключевые слова**: локального заряд, оксидно-полупроводниковая область, плотность электронов и дырок, рn переход, электрическая емкость, затвор, сток и канал.

**Annotatsiya**: Ushbu maqolada biz zatvor ostidagi oksid qatlamidagi qamralgan zaryadning zatvor-stok sigʻimiga ta'sirini oʻrganamiz. Koʻrsatilgandek, oksid qatlamidagi qamralgan zaryad istokga yaqinlashganda, u stok-kanal soxalaridagi elektronlar va kovaklarning zichligi va stok-kanal soxalari sigʻimining oʻzgarishiga ta'sir qiladi.

**Kalit so'zlar:** Qamralgan zaryad, oksid va yarimo'tkazgich soxasi, elektronlar va kovaklar zichligi, p-n o'tish, elektr sig'imi, zatvor stok, kanal.

PACS number(s): 85.00.00,85.30.De

### I. Introduction

At the semiconductor-oxide interface in a metaloxide semiconductor stack, imperfections in the chemical structure lead to interface traps. These localized defects can trap and release mobile charge, leading to drain-current noise [1-2] as well as a reduced electrostatic control of the gate over the channel [3-5]. Interface traps are formed during device processing, but can be additionally created by e.g. ionizing radiation and electrical stress. CMOS process development, process control and reliability assessment require an accurate estimate of the interface state density in these devices. Trapped charges can have a significant impact on the capacitance between the gate and the source layers in FinFETs. Trapped charges can cause a shift in the threshold voltage, which can affect the device's performance, and can also alter the effective capacitance between the gate and the source layers [6]. When charges are trapped in the gate oxide layer of a FinFET, they can alter the effective thickness of the oxide layer, which affects the capacitance between the gate and the

source layers. The trapped charges can act as additional charges that contribute to the capacitance between the gate and the source, and can increase or decrease the effective capacitance depending on their polarity and density. Moreover, the presence of trapped charges can also alter the threshold voltage of the device. The trapped charges can create an electric field that opposes the gate electric field, leading to a shift in the threshold voltage. This shift in the threshold voltage can cause the device to operate at a higher or lower voltage than intended, which can result in performance issues. To mitigate the effects of trapped charges on the capacitance between the gate and the source layers, various techniques may be used, such as incorporating a high-k dielectric material to reduce the density of trapped charges, or using a gate stack engineering technique to reduce the effective thickness of the oxide layer[7]. Additionally, annealing or bias-stress techniques may also be employed to reduce the impact of trapped charges on the device's performance. Annealing is a process that involves heating the FinFET device to a high temperature for a short period of

<sup>&</sup>lt;sup>1</sup>Andijan State University named after Z.M. Babur, 170100 Andijan, Uzbekistan

<sup>&</sup>lt;sup>2</sup>Urganch State University, 220100 Urganch

time. Annealing can help to reduce the effects of trapped charges on the capacitance between the gate and the source layers. During the annealing process, the trapped charges can be neutralized or redistributed, which can reduce their impact on the device's performance. Bias-stress techniques involve applying a voltage bias to the gate of the FinFET for an extended period of time. The application of the bias voltage can cause the trapped charges to move, and the effect of the trapped charges on the device's performance can be measured[8]. By studying the effects of the bias voltage, the impact of trapped charges on the device's performance can be characterized, and steps can be taken to mitigate their effects. Trapped charges can significantly impact the capacitance between the gate and the source layers in FinFETs. The presence of trapped charges can alter the effective thickness of the gate oxide layer, which affects the capacitance between the gate and the source layers. Additionally, trapped charges can also shift the threshold voltage of the device, leading to performance issues. Various techniques such as high-k dielectric material, gate stack engineering, annealing, and bias-stress techniques can be used to mitigate the effects of trapped charges on the device's performance [9]. Nowadays, studying the influence of the accumulated charges in the defects of the gate oxide region via the long-time operation of FinFET is one of the actual problems. The purpose of this paper is to study the influence of the local accumulated charge in the gate oxide layer on the capacitance of gate-drain.

## II. Device structure and simulation conditions

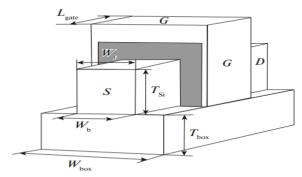

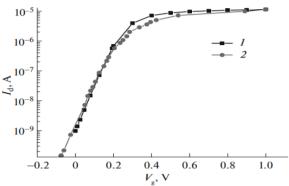

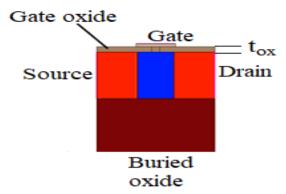

In our research 3D-modeling was carried out using the Advanced TCAD Sentaurus program [10]. The structure of the FinFET studied in this paper by of the simulation is shown in Fig. 1. A diffusion-drift transport model was used in the simulation. The model takes into account the Shockley–Read–Hall recombination and Auger recombination for minority carriers. The mobility model doping dependence and velocity saturation was also included. Since the transistor has a nanometer size, it is necessary to take into account the quantum effects. The most preferred for diffusiondrift simulation is the density gradient quantum correction [11], which was used in this study. The model was calibrated according to the experimental results (Fig. 2) [12].

Fig. 1. The structure of the FinFET studied by of the simulation

Fig. 1. The structure of the FinFET studied by of the simulation

Fig. 1. The structure of the FinFET studied by of the simulation

Fig. 2. Calibration of the I–V characteristic of (1) a simulated transistor by (2) experimental results of at  $L_{gate} = 25$  nm and  $V_{ds} = 50$  mV.

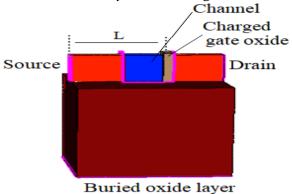

The following structure parameters were used in the simulation. The length of the polysilicon gate (G) doped with phosphorus at a concentration of  $10^{20}$  cm<sup>-3</sup> is L<sub>gate</sub> = 25 nm. HfO<sub>2</sub> with an equivalent thickness of  $t_{ox} = 0.35$  nm is taken as a gate oxide layer. The length and width of the buried oxide layer were  $L_{box} = 75$  nm and  $W_{box} = 100$  nm, respectively. The transistor fin is doped with boron at a concentration of  $10^{15}$  cm<sup>-3</sup>, has the height  $T_{si}$ =30 nm and a base width of  $W_b = 12$  nm, the drain (D) and source (S) regions are doped with phosphorus with a Gaussian profile with a maximal concentration of 10<sup>20</sup> cm<sup>-</sup> <sup>3</sup>. The lengths of the drain and source regions are 25 nm. For study influence the trapped charges in semiconductor-insulator interface to the capacitance between the gate and the source layers. In simulation charged layer has set as fig.3. At here width of charged layer is 5 nm which as shown Fig. 3. Volume bulk density of charge is equal to  $4 \cdot 10^{18}$  C/m<sup>3</sup>.

### III. Simulations results and discussion

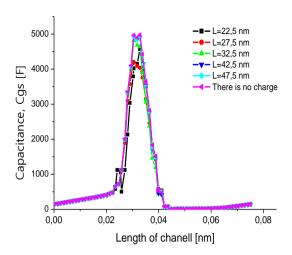

In the simulation, the charged layer moves from drain to source with 5nm step by step as shown Fig. 3. Besides, in the second stage the charged region extended from 5nm to 25 nm step by step. In simulation, the change in capacitance between the gate

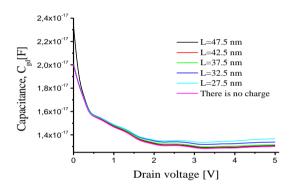

and the drain was studied when the charged gate oxide region moved from the drain to the source when the drain was supplied with a voltage of 5 V. The obtained results are presented in Fig. 4.

Fig. 3. Location of charged gate oxide region and its moving from drain to source with 5nm step.

Fig. 4. The change capacitance between the gate and the drain depending on the located distance of charged gate oxide region

The analysis of the results obtained in Fig. 4. indicates that, there is impact of the local charged region on the gate-drain electric capacity. The change of the gate-drain electric capacity depends on the change of the p-n junction capacity. Because the charged region influences to the depletion region in the p-n junction. For to determine this, we will check the influence of the charged region on the density of electrons and holes in the p-n junction. The obtained results are presented in Fig. 5. and Fig. 6.

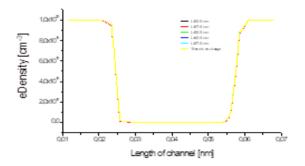

Fig.5. Electron density along the channel 1 nm below the top of the channel

Fig.6. Hole density along the channel 1 nm below the top of the channel

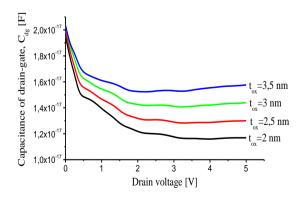

If we analyze the obtained results, the approaching of the charged region to the source side causes a change in the density of electrons and holes in the p-n junction region, we can see it from Fig. 5. and Fig. 6. It is the change in the density of electrons and holes that changes the electric capacity of the pn junction. If the capacitance of the p-n junction changes, the total capacitance of between the gate and drain also changes. But the influence on the total electrical capacity of gate-drain is less than that of the p-n junction electrical capacity. Because the total capacitance of the gate-drain is formed by the series connection capacitance of metal-oxide, capacitance of oxide-semiconductor and capacitance of p-n junction. In this paper, the investigate of the thickness of the gate oxide layer on the capacity of gate-drain is also studied. In simulation prosses, the capacity of drain-gate was calculated in the thickness of the HfO<sub>2</sub> oxide layer from 2 nm to 3.5 nm. The obtained results and the equivalent structure of the vertical field-effect transistor (FinFET) studied in the simulation are shown in Fig. 7. and Fig. 8.

Fig.7. Impact of oxide layer thickness on capacitance of drain-gate

Fig. 8. Equivalent structure of the vertical field-effect transistor.

### IV. Conclusion

Using the obtained results and their discussion can be give as follow main conclusions. The trapped charge at the gate oxide influences the density of electrons, holes in the drain-channel region and capacitance of the p-n junction in the drain-channel region. The approaching of the trapped charge to the source has a stronger influence on the electric capacity of the p-n junction in the drain-channel region. It was determined that the capacitance of drain-gate increases when the thickness of the oxide layer increases.

#### References

- [1] K.K. Hung, P. K. Ko, C. Hu and Y. C. Cheng, "A unified model for the flicker noise in metal-oxide-semiconductor field effect transistors", IEEE Trans. Electron Devices, vol. 37 no. 3, pp. 654-665 (1990).

- [2] G. Ghibaudo, O. Roux, Ch. Nguyen-Duc, F. Balestra, and J. Brini, "Improved analysis of low frequency noise in field-effect MOS transistors", Physica status solidi A, vol. 124, pp. 571-581, 1991.

- [3] D.K. Schroder, "Semiconductor material and device characterization", 3 rd edition, John Wiley & Sons, Inc., USA, 2006.

- [4] S.C. Witczak, J.S. Suehle, and M. Gaitan, "An experimental comparison of measurement techniques to extract Si-SiO2 interface trap density", Solid-State Electronics, vol. 35, no. 3, pp. 345-355, 1992.

- [5] S.M. Sze and K.K. Ng, "Physics of Semiconductor Devices", 3rd edition, John Wiley & Sons, Inc., USA, 2007.

- [6] S. Khandelwal and S. S. Islam, "Impact of gate oxide traps on FinFET threshold voltage and subthreshold slope," Microelectronics Reliability, vol. 54, no. 6-7, pp. 1146-1151, June-July 2014.

- [7] C. Luo, X. Li, and M. Li, "Effect of gate oxide trapped charges on the performance of FinFETs," Journal of Semiconductors, vol. 37, no. 1, pp. 014002-1-014002-6, January 2016.

- [8] Y. Liu, Y. He, X. Zhang, and J. Kang, "Impact of interface trap charge on sub-threshold slope of FinFET," Chinese Physics Letters, vol. 33, no. 4, pp. 047301-1-047301-4, April 2016.

- [9] S. Gupta, R. P. Agarwal, and D. Gupta, "Effect of gate oxide trapped charges on the performance of FinFET-based SRAM cells," Journal of Computational Electronics, vol. 16, no. 4, pp. 1162-1172, December 2017.

[10] www.synopsys.com.

- [11] A. E. Abdikarimov, A. G. Indalecio, E. Comesana, N. Seoane, K. Kalna, A. J. García-Loureiro, and A. E. Atamuratov, in Proceedings of the 17th International Workshop on Computational Electronics, Paris, France, 2014, p. 247. http://www.iwce.org/iwce/browse/iwce17/abstracts.html.

- [12] V. S. Basker, T. Standaert, H. Kawasaki, C.-C. Yeh, K. Maitra, T. Yamashita, Y. Faltermeier, H. Adhikari, H. Jagannathan, J. Wang, H. Sunamura, S. Kanakasabapathy, S. Schmitz, J. Cummings, A. Inada, et al., in Proceedings of the Symposium on VLSI Technology (IEEE, 2010), p. 19.

**Theme of article:** Influence of the local trapped charge in oxide to the gate - drain capacitance in a finFET

Authors: M.B. Foziljonov, I. N. Karimov, A.E.Abdikarimov

*Address:* 129 st.Universitet, Andijan city, Republic of Uzbekistan, 170100

**Summary:** In this paper, the influence of the local trapped charge in the gate oxide layer on the total of the capacity of gate-drain is studied. It was investigated that the approaching of the local trapped charge in the gate oxide layer towards the source influences the change in the density of electrons and holes in the drain-channel regions and electric capacity of drain-channel regions.

**Keywords:** trapped charge, oxide-semiconductor region, density of electrons and holes, p-n junction, electric capacity, gate, drain and channel.

### Information about the authors

**A.E.Abdikarimov** Physics department Urgench State University

Pochta: abdukarimov.azamat@rambler.ru

Tel: +998995909376

**M.B. Foziljonov** Physics department Andijan State University

Pochta: foziljonov.mirzabahrom.1991@gmail.com Tel:+998999037009

I. N. Karimov Physics departmentAndijan State University

Pochta: ibroximjon.karimov1956@gmail.com Tel: +998900607578